Student teams earn prizes for their ADC circuit designs in EECS 511

The two winning projects and teams were determined by an expert panel at Analog Devices. Congratulations!

Enlarge

Enlarge

Students in the graduate level course, Integrated Analog/Digital Interface Circuits (EECS 511), taught by Prof. Michael Flynn, competed for cash prizes while presenting their final design projects thanks to the support of Analog Devices, Inc. Two winning projects and teams were determined by an expert panel at Analog Devices.

First Place ($1,500)

A 1GS/s 7-bit low power, time-interleaved Asynchronous SAR ADC, by Nan Zheng, Yiqun Zhang, and Laura Freyman

Enlarge

Enlarge

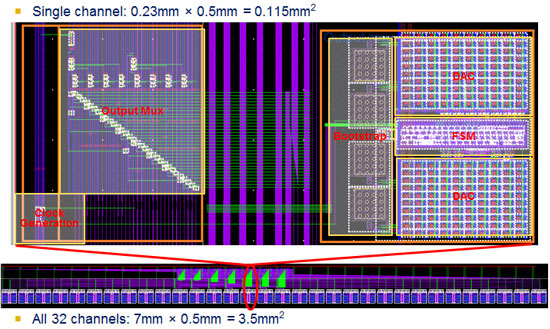

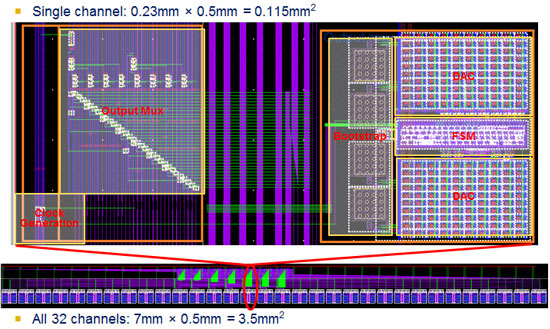

In numerous wideband communication systems, high-speed and low-power analog-to-digital converters (ADCs) are needed to sample the data in an energy-efficient manner. While traditional flash ADCs achieve fast sampling speeds, they fail to fulfill all of the given requirements due to their limited resolution. In this project, a 1GS/s 7-bit time-interleaved asynchronous successive-approximation-register (SAR) ADC was designed and implemented. It meets both the resolution and speed requirements by time-interleaving 32 low-power asynchronous SAR ADCs.

Analog off-line calibration methods have been studied in this project to cancel inter-channel mismatches that potentially exist in the 32 channels. Digital logic operates at 0.6V and analog circuitry at 1.2V, with a total power dissipation of 4.7 mW, ENOB of 5.6 bits, and FOM of 96 fJ/conv-step at a sampling frequency of 1GHz.

Second Place ($500)

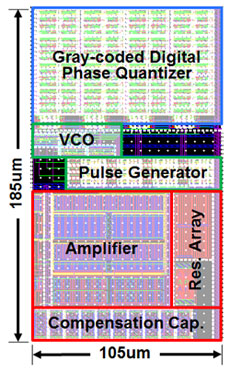

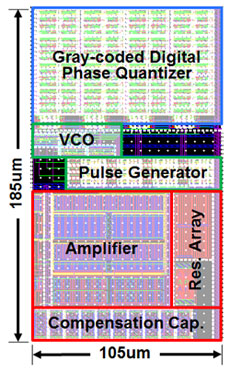

A Frequency Linearized VCO-based Analog-to-Digital Converter, by Tae-Kwang Jang, Sunmin Kim, and Myungjoon Choi

Enlarge

Enlarge

Enlarge

Enlarge

Designing analog-to-digital converters with high resolution gets more and more difficult due to the reduced supply voltage, increased noise and poor matching. Voltage-controlled oscillator (VCO)-based ADCs, however, use time information to convert the analog voltage to digital code, which achieves increasingly better performance in the advanced processes. However, limitations on the linearity and time resolution greatly affect the overall performance of the ADC.

In this work, a frequency regulation loop using a pulsed resistor feedback is proposed to improve the linearity. A wide tuning range VCO combined with a 2:1 phase interpolator is designed to achieve high resolution. A gray coded counter based digital phase quantizer is also proposed in order to reduce the sampling frequency, thus the power consumption.

The proposed VCO-based ADC, designed in 130nm CMOS process, achieved 51.5dB SNDR while consuming 6.12mW when the sampling frequency and the signal bandwidth are 500MHz and 4MHz, respectively. The core area is 0.019 mm2.

MENU

MENU